# Bistabile Kippstufen in der Digitaltechnik

(Flipflop, Folgeschaltungen)

ES UZ

### 1 Prinzip

Bei den in FtA Es of behandelten Grundschaltungen (UND. ODER, NAND, NOR) ist das Ausgangssignal dadurch bestimmt, nelche Signale im betrachteten Zeitpunkt an den Eingängen liegen. Die bistabilen Kippstufen dagegen haben Speichereigenschaft. Der Signalzustand am Ausgang kann in dem betrachteten Zeitpunkt von den anliegenden Eingangssignaler und/oder von einem Eingangssignal-zustand bestimmt sein, der vor diesem Zeitpunkt vorhanden nor. Das heißt, der zu einer Zeit it durch entsprechende Eingangssignale erzeugte Ausgangszustand bleibt erhalten, auch wenn in der Zwischenzeit die Eingangssignale abgeschaltet oder geändert wurden.

Man spricht deshalb von Folgeschaltungen, Zeitfolgeschaltungen [sequentiell network]. Ihr besonderes Kennzeichen ist das Vorhandensein einer Rückkopplung vom Ausgang zum Eingang. Die einfachste Zeitfolgeschaltung ist das Flipflop, Mit diesem Ausfruck soll, wie bekannt, angedeutet werden, daß am Ausgang lediglich ein Wechsel zwischen zwei definierten Signalzuständen (flip und flop) erfolgen kann. Seine Eigenschaften:

Beide Zustände sind stabil. Der Wechsel erfolgt durch ein entsprechendes Eingangssignal oder eine Kombination verschiedener Eingangssignale. Der eingestellte Zustand, ausgedrückt durch das Ausgangssignal, kann aber auch trotz Einangssignaländerung gespeichert bleiben. Erwähnt sei, daß natürlich bei Störungen in der Stromversorgung die gespeicherte Information verloren geht.

#### 2 Aufbau

2715

Im allgemeinen verwendet man dafür zwei NAND- oder zwei NOR-Glieder. Eine solche Schaltung ist symmetrisch. Jedes der Glieder erzeugt eine Phasendrehung von 180°, die Drehung über zwei Stufen ist also 360° bzw. 0°. Steht am Ausgang Q<sub>1</sub> das L-Signal, dann steht an Q<sub>2</sub> das O-Signal, d. h. die Ausgangssignale sind antivalent<sup>1</sup>.

#### 2.1 Das NAND-Flipflop

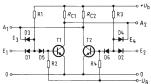

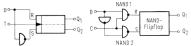

Es wird aus zwei NAND-Gliedern (-Gattern), wie sie in FtA Es 01, Bild 12, gezeigt sind, aufgebaut (Bild 1).

Die Bedingung für ein NAND-Ciled lautet (s. Es 01, Abchnitt 4.3): An der Ausgangsklemme eines NAND-Gliedes erscheint nur dann der Signalspannungswert O, wenn an allen Eingangsklemmen der Signalspannungswert L liegt. Diese Bedingung wird durch die Schaltung von Bild 1 erfüllt. Nur, wenn an E, und E3 die Spannung U, steht, sind die Dioden D1, und D3 gespert und der Transistor T1, erhält über R1, D5 eine positive Basisspannung, so daß er leitend wird und an seiner Ausgangsklemme A2 die Spannung O v steht.

Das Ümschalten von dem einem stabilen Zustand in den anderen läuft in folgender Weise ab: Als Beispiel dafür sei 1) Die Ausgänge werden teils mit A<sub>1</sub>, A<sub>2</sub>, mit Q<sub>1</sub>, Q<sub>2</sub> oder mit Q, Q̄ bezeichnet. In Es 62 wird generell die positive Logik angewendet (s. Es 61, Abschn. 6).

Bild 1. Schaltung eines NAND-Flipflops.  $E_1$  und  $A_1$ , bzw. R und  $Q_1$  sind einander so zugeordnet, daß ein L am Eingang eines Feldes (Bild 2 rechts) ein L am Ausgang desselben Feldes bewirkt

der bereits erwähnte Zustand angenommen, daß sich Transistor  $T_1$  im leitenden und Transistor  $T_2$  im gesperrten Zustand befinden, d, h.

an E<sub>1</sub> liegt + U<sub>b</sub>

an E<sub>2</sub> 0 V T<sub>2</sub> gesperrt

T<sub>1</sub> ist leitend,

11 1st leitend, 12 gesperrt  $A_2$  (E4) führt die Spannung 0 V,  $A_1$  (E3) die Spannung  $U_b$ .

Nun wird an  $E_1$  0 V, an  $E_2$  +  $U_b$  gelegt.  $D_1$  wird leitend, so daß an der Basis von  $T_1$  nun –  $U_b$  steht. Dadurch wird  $T_1$  gespert und  $A_2$  ( $E_d$ ) erhilt die Spannung +  $U_b$ . Da nun die beiden Dioden  $D_2$  und  $D_4$  gespertr sind, bekommt die Basis von  $T_2$  positive Spannung über  $R_3$ ,  $D_6$ . Der Transistor  $T_2$  wird leitend und die Spannung an  $A_1$  ( $E_3$ ) of

Man beachte, daß ein NAND-Flipflop nur durch den Signalspannungswert O an einem der Eingänge umgeschaltet werden kann.

Bild 2. Funktionsplan und Schaltzeichen für ein NAND-Flipflop

Die Schaltzustände eines NAND-Flipflops

| E <sub>2</sub> | E <sub>1</sub> | $Q_1$            | Q <sub>2</sub> |  |  |  |  |

|----------------|----------------|------------------|----------------|--|--|--|--|

| 0              | 0              | L                | L              |  |  |  |  |

| 0              | L              | L                | о              |  |  |  |  |

| L              | l o            | О                | L              |  |  |  |  |

| L              | L              | Speicherstellung |                |  |  |  |  |

Speicherstellung heißt: Der Schaltzustand ändert sich nicht, der vorhergehende Zustand bleibt erhalten.

Verkörpert man die NAND-Glieder durch ihre Schaltzeichen, erhält man Bild 2.

#### 2.2 Das NOR-Flipflop

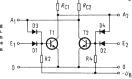

Es wird aus zwei NOR-Gliedern (-Gattern), wie sie in Es 01, Bild 15 gezeigt sind, aufgebaut (Bild 3).

Die Bedingung für ein NOR-Glied lautet (s. Es 01, Abschnitt 5.3): An der Ausgangsklemme des NOR-Gliedes erscheint der Signalspannungswert O, wenn nur an einer Ein-

gangsklemme der Signalspannungswert L liegt, Diese Bedingung wird durch die Schaltung von Bild 3 erfüllt. Denn, wenn an  $E_1$  die Spannung  $U_b$  liegt, erhält der Transistor  $T_1$  eine positive Basisspannung, er kommt in den leitenden Zustand und die Spannung  $A_2$  wird 0 V.

Die Umschaltung in den zweiten, stabilen Zustand geschieht in folgender Weise.

An  $E_1$  wird 0 V, an  $E_2 + U_b$  gelegt. Der Transistor  $T_2$  erhält eine positive Basisspannung, denn D ist gesperrt, da  $A_2$  noch die Spannung 0 V führt.  $T_2$  wird demnach leitend und die Spannung an  $A_1$  0 V. Nun wirkt über  $R_2$  die Spannung  $-U_b$  auf die Basis des Transistors  $T_1$  und sperrt ihn, so daß an  $A_2$  der Signalspannungswert L erscheint.

Man beachte, daß ein NOR-Flipflop nur durch den Signalspannungswert L an einem der Eingänge umgeschaltet werden kann.

Die Schaltzustände eines NOR-Flipflops

| $E_2$ | E <sub>1</sub> | $Q_1$    | $Q_2$    |

|-------|----------------|----------|----------|

| 0     | 0              | Speicher | stellung |

| L     | 0              | О        | L        |

| 0     | L              | L        | 0        |

| L     | L              | 0        | 0        |

$Bild\ 4$  zeigt das NOR-Flipflop, dargestellt mit Digitalschaltzeichen.

#### 3 Eingangsschaltungen

Man unterscheidet:

statisch und dynamisch wirkende Eingangsschaltungen. Im Fall der statisch wirkenden Eingangsschaltungen besteht Gleichstromkopplung zwischen der Signalquelle und dem

angesteuerten Verküpfungsglied.

Eine dynamisch wirkende Eingangsschaltung spricht auf den Spannungssprung bei Übergang von dem einen in den anderen Signalzustand an. Das Ansprechen kann einem O - L-Übergang (ansteigende Flanke) oder bei einem L - O Übergang (abfallende Flanke) erfolgen. Maßgeblich für das Ansprechen ist die Änderungsgeschwindigkeit. Solche "dynamischen Eingänge" nennt man Impuls- oder Triggereingänge. Ihre Aufgabe wird schon durch das Wort "Trigger" angedeutet, soll aber an einem einfachen Beispiel erlätuert werden.

# 3.1 Impuls- oder Triggergatter, Impuls- oder Triggereingang

Diese Schaltungen haben zwei Eingänge:

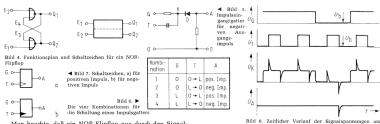

einen statischen oder Vorbereitungs-Eingang G, einen dynamischen oder Impuls-Eingang T (Bild 5).

Die Ausgangsspannung ist von dem Zustand an G und von der Änderungsgeschwindigkeit des Signalspannungswertes am Eingang T, also von du/dt, abhängig.

Aus der Schaltung von Bild 5 ist folgendes abzulesen. Liegt an G der Signalspannungswert L, ist die Diode D gespert. Sie ist dagegen leitend, wenn an G die Spannung 0 V steht. Ein Spannungsprung von O  $\rightarrow$  L wird von D gespert, ein Sprung von L  $\rightarrow$  O dagegen rezeugt an A (für G = O), einen negativen Impuis. Diese Abhänigiskeit kann in einem Zeitdiagramm (Bild 6) dargestellt werden.

Ein solches Gatter wirkt wie eine UND-Verknüpfung zwischen G und T. Das dafür verwendete Schaltzeichen bringt Bild7. Das Schaltzeichen mit unausgefüllter Pfeilspitze bedeutet einen Sprung von  $O \rightarrow L$  (Bild 7o), mit ausgefüllter Pfeilspitze einen Sprung von  $L \rightarrow O$  (Bild 7b). Es gibt naturgemäß vier Kombinationen für solche Impulsgatter (Bild B).

### 4 Asynchroner und synchroner Betrieb von Flipflops in Netzwerken

Ein ohne zusätzlichen Impulseingang betriebenes Flipflog schaltet im Prinzip sofort nach Anlegen der Eingangssignale. Allerdings tritt eine, normalerweise nicht störende, Schaltverzögerung (Laufzeitverzögerung) auf. Sie kann dann aber störend sein, wenn in Netzwerken Flipflops in Ketten hintereinander und parallel geschaltet werden. Denn bei einer Serienschaltung werden Flipflops nicht gleichzeitig, sondern es wird eins nach dem anderen geschaltet. (asynchroner Betrieh)

Impulsgatter von Bild 5

Abhilfe kann man dadurch schaffen, daß die Flipflops je einen Impulseingang erhalten. Diese werden mit Taktimpulsen so gesteuert, daß die Flipflops zu vorgegebenen Zeitpunkten schalten (synchroner Betrieb).

Die Vorbereitungseingänge müssen dann nicht nur vorbeeitend, sondern auch speichernd wirken, d. h. sie müssen das Vorbereitungssignal so lange speichern, bis der Taktimpuls das Flipflop geschaltet hat, also der Signalspannungswert des G-Eingangs in den Speicher gesetzt ists.

Ferner muß die Zeit zwischen zwei Taktimpulsen größer als die Schaltverzögerung in den betrachteten Stufen sein.

#### 5 Flipflop-Arten

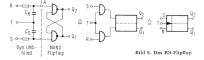

# 5.1 RS-Flipflop (auch SR-Flipflop genannt)

Die Bezeichnung RS leitet sich ab aus: set = setzen und reset = löschen. Dieses Flipflop setzt sich aus zwei Schaltungsteilen zusammen, einem NAND-Flipflop und einer zusätzlichen Verknüpfungsschaltung für die Vorbereitungseingänge R/S und den Takteingang T. also einem Triggergatter. Ein Beispiel dafür zeigt Bild 9. Das Triggergatter liefert einen negativen Impuls, mit dem das Flipflop geschaltet wird.

Es liege am Eingang R die Spannung 0 V, am Eingang S dagegen Uh, der Impuls an T springe von 0 V auf Uh, dann lädt sich  $C_R$ , wie in Bild 9a angegeben, auf.  $C_S$  dagegen entlädt sich, da an beiden Anschlüssen jetzt die Spannung Uhlegt. Beim Zurückspringen des Taktimpulses auf den Wert 0 V erhält der R-Eingang kurzzeitig die Spannung —Uhlid 19b, das NAND-Filplop wird geschaltet. Der Vorteil des getakteten Schaltens besteht nicht nur darin, daß der Schaltvorgang zu einem vorgegebenen Zeitpunkt, wie für synchronen Betrieb erforderlich, erfolgt, sondern daß auch die Störungen auf diesen Eingängen spielen nur im Zeitpunkt des Schaltens eine Rolle.

# 5.2 Das D-Flipflop (delay-flipflop)

Dieses Flipflop besitzt nur einen Vorbereitungseingang D. Wie Bild 10 zeigt, ist der Eingang D mit R direkt, mit S dagegen über eine Umkehrstufe verbunden. Die jeweils am Eingang D liegende Information wird bei dem nächstfolgenden Taktimpuls im Flipflop gespeichert. Diese Tatsache kann man auch aus der Funktionstabelle ablesen. Sie lautet für das D-Flipflop:

| $\mathbf{D}_{\mathrm{n}}$ | Qn+1 |

|---------------------------|------|

| О                         | 0    |

|                           |      |

Mit n wird der Zustand eines Signals zum Zeitpunkt  $t_n$  (n-ter Taktimpuls), mit n + 1 zum Zeitpunkt  $t_{n+1}$ , also des nächsten auf  $t_n$  folgenden Taktimpulses, angegeben.

Bild 100 zeigt, wie das Impulsgatter (die Steuerschaltung) gestaltet sein muß, damit die Bedingungen der Funktionstabelle erfüllt werden. Die an wichtigen Punkten der Schaltung auftretenden Signalspannungswerte zeigt Tabelle 1. Sie ist unter Zuhlfenahme der Tabellen von Abschnitt 2.1 und von Es 01, Abschnitt 4.4 erarbeitet. Man sieht, daß die Bediungen der Funktionstabelle erfüllt werden, und daß das Impulsgatter mit NAND-Gliedern bestückt werden muß, damit im Fall C & O an beiden Eingängen des NAND-Flipflops L-Signale auftreten und dieses deshalb in Speicherstellung bleibt. Dieses D-Flipflop wird für Schieberegister verwendet.

Tabelle 1.

| D-Ein-<br>gang | C-Ein-<br>gang | ga<br>NA | n-<br>ng<br>ND- | NA  | ng<br>ND- | Flip-<br>flop-<br>Ein-<br>gang | Flip-<br>flop-<br>Ein-<br>gang |       | flop-<br>gang  |

|----------------|----------------|----------|-----------------|-----|-----------|--------------------------------|--------------------------------|-------|----------------|

|                |                | Gli      | ed 1            | Gli | ed 2      | s                              | R                              | $Q_1$ | $Q_2$          |

| L              | L              | L        | L               | 0   | L         | 0                              | L                              | L     | 0              |

| 0              | L              | 0        | L               | L   | L         | L                              | 0                              | О     | L              |

| L              | 0              | L        | О               | О   | О         | L                              | L                              |       | icher-<br>lung |

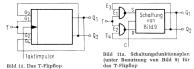

# 5.3 Das T-Flipflop (Trigger-Flipflop)

Die Schaltung ergibt sich aus Bild 11. Man erkennt, daß dem Flipflop zwei Impulsgatter mit je zwei Vorbereitungseingängen  $G_1$ ,  $G_3$  und  $G_2$ ,  $G_4$  vorgeschaltet sind. Dabei ist

G4 mit Q1, ferner G3 mit Q2 verbunden

und G1 bildet mit G2 den Anschluß T.

Über den Impulseingang wird der Taktimpuls zugeführt. Man beachte, daß hier mit T nicht der Eingang für die Taktimpulse bezeichnet wird, Um Verwechslungen zu vermeiden, wurde hier die in der Literatur übliche Bezeichnungsweise übernommen, wonach T der gemeinsame Anschluß für zwei Vorbereitungseingänge ist.

Die Arbeitsweise des T-Flipflops ist folgende: Liegt an T der Signalspannungswert O, ändert sich der Ausgangszustand nicht. Liegt aber der Wert L an T, kippt das Flipflop bei jedem Taktimpuls von dem einen stabilen Zustand in den anderen. Man erhält nachstehende Funktionstabelle:

| $T_n$ | $Q_{n+1}$ |

|-------|-----------|

| 0     | Qn        |

| T     | ō         |

$\overline{Q}_n$  ist der antivalente Zustand zu  $Q_n.$  Ist z. B.  $Q_n=L$  , ist  $\overline{Q}_n=O$  und umgekehrt.

Um diese Arbeitsweise zu erreichen, sind, wie Bild 11a zeigt, dem RS-Flipflop zwei NAND-Glieder vorzuschalten. Dann erhält man beim Schalten von T folgende Signalspannungswerte:

| T | $E_3$ | $E_4$ | S | R | Q <sub>1</sub>  | $Q_2$ |  |

|---|-------|-------|---|---|-----------------|-------|--|

| - |       | -     | - | - | L*)             | O*)   |  |

| L | 0     | L     | L | 0 | 0               | L     |  |

| 0 | L     | 0     | L | L | Speicherstellun |       |  |

| L | L     | 0     | О | L | L               | О     |  |

## \*) Angenommener Ausgangszustand

Man benützt dieses Flipflop für Zählschaltungen. Da das T-Flipflop erst nach jedem zweiten Taktimpuls wieder in die Ausgangslage kommt, arbeitet es auch als Binäruntersetzer für die Taktfrequenz. Bild 9a, b. Die Entstehung des negativen Impulses beim RS-Flipflon

Bild 10. Das D-Flipflop

Bild 10a. Schaltungsfunktionsplan für das D-Flipflop

## 5.4 JK-Flipflop

Dem JK-Flipflop fällt die Aufgabe zu, ein Speicherelement darzustellen, das möglichst universal angewendet werden kann. Es wird wie das T-Flipflop aufgebaut (Abschnitt 5.3), aber die beiden Vorbereitungs-

eingänge  $E_1$  und  $E_2$  werden nicht zu einem, T genannt, zusammengefaßt, sondern getrennt herausgeführt. Damit lassen sich folgende Flipflops nachbilden:

ende Flipflops nachbilden: Das T-Flipflop, wenn man E<sub>1</sub> und E<sub>2</sub> gemeinsam ansteuert,

Bild 12a; das RS-Flipflop, wenn man E<sub>1</sub> und E<sub>2</sub> getrennt ansteuert,

das D-Flipflop, wenn man ein

Umkehrglied vorsetzt, Bild 12c.

Das JK-Fliplop findet man

noch in einer anderen Ausfülrungsform, nämlich dann, wenn

es in monolithisch integrierter

Form gefertigt wird. Bei dieser

Technik bereitet es große

Schwierigkeiten, die für Triggereingänge notwendigen Kapazitäten darzustellen. Man muß

also einen anderen Weg suchen,

schaft haben muß (s. Abschnitt 4).

To  $Q_1$ a C Taktimpulse

Bild 12, a = Das JK-Flipflop, verwendet als T-Flipflop; b = das JK-Flipflop, verwendet als RS-Flipflop; c = das JK-Flipflop, verwendet als D-Flipflop

um die Verknüpfung zwischen Vorbereitungssignal und Taktsignal zu erreichen. Man verwendet "Zwei-Speicher-Schaltungen":

Der zu einer solchen Anordnung führende Gedanke ist insofern nicht überraschend, als ja ein Impulseingang neben seiner UND-Verknüpfung auch noch eine speichernde Eigen-

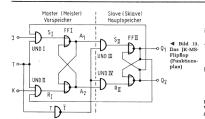

# 5.5 JK-Master/Slave-Flipflop, JK-MS-Flipflop

Die Information wird vom Eingang in zwei Schritten in den Hauptspeicher gesetzt. Der erste Schritt erfolgt bei dem Signalspannungswert L des Taktimpulses, die Information gelangt in den Vorspeicher. Geht der Taktimpuls auf den

Wert O, erfolgt der zweite Schritt, und die Information gelangt in den Hauptspeicher.

Es sind keine steilen Flanken für das Taktsignal erforder-

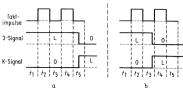

Bild 13 bringt ein Beispiel für den Aufbau eines solchen Flipflops. Die Tabelle 2 zeigt, welche Signalspannungswete sich zu verschiedenen Zeiten an verschiedenen Stellen der Schaltung einstellen. Dabei wird durch Bild 14 deutlich gemacht, welche Bedeutung die Zeitangaben in der Tabelle t<sub>1</sub>...t<sub>4</sub> haben. Im Fall a habe sich (Annahme) im Zeitpunkt t<sub>4</sub> die Kombination der Werte für J und K nicht geändert, im Fall b dagegen sei eine Änderung zur Zeitt serfolgt.

Im einzelnen ist aus der Tabelle 2 abzulesen:

Zeitpunkt t<sub>1</sub>: Die Signalspannungswerte O, L am Ausgang sind angenommen.

Zeitpunkt 1g: Mit diesem Taktimpuls wird die JK-Information in FF I gespeichert. FF II wird dagegen nicht geschaltet, da an seinem Eingang die Wertekombination O, O steht und FF II deshalb in Speicherstellung verharrt.

Bild 14. Schaltfolgediagramm für das JK-MS-Flipflop, dargestellt ist der Verlauf der Signalspannungswerte am Impulseingang und den JK-Eingängen

Zeitpunkt t3: Im FF I ändert sich nichts, aber FF II wird jetzt umgeschaltet.

Zeitpunkt t4: Im Fall a (s. o.) ändert sich nichts. FF I verbleibt in seiner Speicherstellung, im Fall b dagegen wird die neue IK-Information

in FF I gesetzt, FF II behält noch seinen alten

Zustand.

Zeitpunkt t5: Im Fall b wird nun die geänderte Information an den Eingängen JK in das FF II gesetzt.

## Literatur

Dokter, F., und Steinhauer, J.: Digitale Elektronik in der Meßtechnik und Datanverarbeitung. Philips Fachbücher, Deutsche Philips GmbH, Hamhure.

Elektronik-Arbeitsblatt Nr. 47. Bistabile Kippstufen aus NAND- und NOR-Schaltungen. Franzis-Verlag, München.

Digitale integrierte Schaltungen. Telefunken-Fachbuch, Elitera Verlag, Berlin.

Korthals Altes, J. Ph., und Schanz, G. W.: Logische Schaltungen mit Transistoren. Philips Taschenbücher, Deutsche Philips GmbH, Hamburg. Schaltzeichen der Digitaltechnik und ihre Bedeutung. Funktechnische Arbeitsblätter Es 01. Franzis-Verlag, München.

Tabelle 2. Signalspannungswerte am JK-MS-Flipflop (s. Bild 13 und 14)

|                     |   | UND   | -Glie          | d I          | 1     | UND     | -Glied           | l II         | Flip                            | flop I                        | UND-G                 | ied III               | UND-Glied IV Flipflo                              |                         |                                 |                         |

|---------------------|---|-------|----------------|--------------|-------|---------|------------------|--------------|---------------------------------|-------------------------------|-----------------------|-----------------------|---------------------------------------------------|-------------------------|---------------------------------|-------------------------|

| Zeit<br>t           | Е | ingar | ng             | Aus-<br>gang | Е     | ingai   | ng               | Aus-<br>gang | Eingang                         | Ausgang                       | Eingang               | Aus-<br>gang          | Eingang                                           | Aus-<br>gang            | Eingang                         | Ausgang                 |

|                     | J | Т     | $\mathbf{Q}_2$ | SI           | K     | Т       | $\mathbf{Q}_{1}$ | RI           | R <sub>I</sub> S <sub>I</sub>   | A <sub>1</sub> A <sub>2</sub> | $A_1 \overline{T}$    | SII                   | A <sub>2</sub> T                                  | RII                     | R <sub>II</sub> S <sub>II</sub> | $Q_1$ $Q_2$             |

| $t_1$               |   | _     |                | _            |       | -       |                  | _            |                                 | -                             | _                     | _                     | _                                                 | _                       | _                               | OLL                     |

| <b>t</b> 2          | L | L     | L              | L            |       |         |                  |              | L                               | 0                             | 0 0                   | 0                     |                                                   |                         | O<br>Speicher-<br>stellung      | o₩                      |

|                     |   |       |                |              | 0     | L       | 0                | 0            | 0                               | L                             |                       |                       | r o                                               | 0                       | 0                               | L                       |

| t <sub>3</sub>      | L | O     | L              | 0            | 0     | 0       | 0                | o            | O<br>Speicher-<br>stellung<br>O | OV<br>L                       | O T                   | 0                     | L L                                               | L                       | O                               | L                       |

| t <sub>4</sub>      | L | L     | 0              | 0            | 0     | L       | L                | 0            | O<br>Speicher-<br>stellung<br>O | O                             |                       | eitpunk               | ung am A<br>it t <sub>5</sub> , da k<br>n Eingäng | eine Ä                  | nderung                         |                         |

| t <sub>4</sub><br>b | 0 | L     | 0              | 0            | L     | L       | L                | L            | O<br>L                          | L O                           | L O                   | 0                     | 0 0                                               | 0                       | O<br>Speicher-<br>stellung<br>O | r 🗸                     |

| t <sub>5</sub>      | 0 | 0     | 0              | 0            | T.    | 0       | T.               |              | stellung                        | r \                           | L L                   | L                     | 0 1                                               | 0                       | L                               | O                       |

|                     | 0 | _     | )              | 0 0          | 0 0 0 | D O O L |                  |              |                                 | Speicher-<br>stellung         | Speicher-<br>stellung | Speicher-<br>stellung | Speicher-<br>stellung                             | Speicher-<br>stellung > | Speicher-<br>stellung           | Speicher-<br>stellung > |