# Elektronische Zähler

2 Blätter

### 1 Einleitung

Es braucht wohl nicht besonders begründet zu werden, daß der elektronische Zähler zu den wichtigsten Bauelementen/Baugruppen in der Elektronis gehört. Aus diesem

Grunde ist nicht nur seine Anwendung, sondern auch seine

Aufbautechnik sehr vielgestaltig. Hier soll nur von Zählern

gesprochen werden, die Flipflops (bistabile Kippstufen) als

Speicherelemente benützen. Bevor die Funktionsweise eines

solchen Zählers behandelt wird, soll auf seinen wichtigen

Baustein, nämlich den Speicher in Form einer bistabilen

Kippstufe, eineseangen werden.

Ein Zähler muß addieren und speichern. Denn bei jedem Zählschritt wird ein bestimmter Wert zu dem gespeicherten Wert hinzuaddiert.

Man benutzt das duale Zahlensystem. Das bedeutet, man bildet Summen von Zweierpotenzen. Die Dezimalzahl 23 wird demnach dargestellt durch:

$$1 \times 2^{4} + 0 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}$$

und geschrieben

Zur elektronischen Realisierung dieses Zählvorgangs benötigt man ein Bauteil, das Zählimpulse zählen und die jeweils erreichte Summe speichern kann. Dazu eignet sich das Flipflop (heute, nach DIN 41859 Bl. 2, bistabile Kippschaltung genannt), denn es kann einen Schaltungszustand beliebig lange festhalten, also speichern.

Für jede Zweierpotenzstufe benötigt man ein Flipflop. Es muß dann dafür gesorgt sein, daß der Speicherinhalt, wenn die Speicherkapazität erschöpft ist, in den Speicher der nächst höheren Zweierpotenz übertragen wird:

## 2 Das JK-Flipflop

Von den verschiedenen Flipflop-Typen (RS-, D-, T-, JK-Flipflop) wird das Letztgenannte aus folgenden Gründen gewählt:

Zunächst braucht man ein taktpulsgesteuertes Flipflop. Das bedeutet, daß die Information den Vorbereitungseingängen [J, K] zugeführt, aber erst durch den Taktimpuls in das Flipflop übernommen wird. Der Taktimpuls hat also auslösende Wirkung.

Dann braucht man ein Zweispeicher-Flipflop.

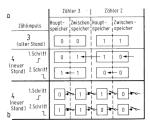

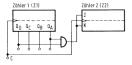

Diese Forderungen ergeben sich aus der Zähltechnik. Wir betrachten dazu drei Zählereinheiten und wählen das Dualsystem. Am Zählbeginn stehen alle Zähler auf 0. Mit dem  Zählimpuls geht Zähler 1 auf 1, alle übrigen Zähler zeigen 0. Mit dem 2. Zählimpuls wird Zähler 1 wieder auf 0 gesetzt, sein Speicherinhalt, nämlich die 1, wird in den 2. Zähler übertragen, so daß also Zähler 1 die 0, Zähler 2 die 1, Zähler 3 die 0 anzeigt (Bild 1).

Man muß beachten, daß bei einem Taktimpuls sowohl eine neue Information eingespeichert als auch die vorher vorhandene abgefragt (übertragen) werden muß. So muß z. B. (Bild 1) bei dem Zählimpuls 4 der Zähler 2 die eingespeicherte 1 auf Zähler 3 übertragen (da die Speicher der beiden Zähler 2 und 1 gefüllt sind) und anstelle der 1 eine 0 einspeichern.

Die beiden Vorgänge "abfragen" und "einspeichern" müssen zeitlich nacheinander ablaufen, damit nicht die eingespeicherte und weiterzugebende Information durch die neue, einzuspeichernde zerstört wird. Hat man ein Zweispeicher-Flipflop, so läßt sich diese Forderung, wie Bild 2 zeigt, leicht erfüllen. In diesem Bild ist der Speicherstand von Zähler 2b beim Übergang von dem Zustand nach Zählimpuls 3 auf den nach zählimpuls 3 erwischenspeicher (Master-Flipflop) die an den Vorbereitungseingängen stehende Information übernimmt, wenn am Takteingang des JK-Flipflops der Signalwert H steht. (Also nach Bild 2:

Zwischenspeicher 2 übernimmt die 0 Zwischenspeicher 3 übernimmt die 1.)

Der Hauptspeicher (Slave-Flipflop) ist dagegen geöffnet, wenn am Takteingang ein L-Signal steht. Diese unterschiedliche Arbeitsweise von Zwischen- und Hauptspeicher ergibt sich daraus, daß das Taktsignal der UND-Verknüpfung des Zwischenspeichers direkt, der UND-Verknüpfung des Hauptspeichers dagegen über einen Inverter zugeführt wird. (Also nach Bild 2:

Hauptspeicher 2 übernimmt vom Zwischenspeicher 2 die 0 Hauptspeicher 3 übernimmt vom Zwischenspeicher 3 die 1.]

Zusätzlich sorgt man noch dafür, daß die Schaltschwellen der beiden Flipflops etwas gegeneinander versetzt sind, so daß der Hauptspeicher erst öffnet, wenn der Zwischenspeicher mit Sicherheit gesperrt ist.

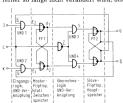

## 2.1 Aufbau eines JK-Flipflops

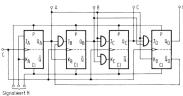

Bild 3 zeigt, wie sich das JK-Flipflop aus dem Master (Vorspeicher, Zwischenspeicher) und dem Slave (Hauptspeicher) zusammensetzt. Jede Teileinheit besteht aus dem als Speicher wirkenden Flipflop (NAND- oder NOR-Flipflop) und der jeweiligen Eingangs-Verknüpfung, dem Übernahme-Gatter, bestehend aus UND- oder NAND-Gliedern.

| Zählimpuls | Zähler 3<br>Z <sup>2</sup> | Zähler 2 | Zähler 1<br>Z <sup>0</sup> |

|------------|----------------------------|----------|----------------------------|

| 0          | 0                          | 0        | 0                          |

| 1          | 0                          | 0        | 1                          |

| 2          | 0                          | 1        | 0                          |

| 3          | 0                          | 1        | 1                          |

| 4          | 1                          | 0        | 0                          |

| 5          | 1                          | 0        | 1                          |

| 6          | 1                          | 1        | 0                          |

| 7          | 1                          | 1        | 1                          |

◀ Bild 1. Der Vorgang des Zählens nach dem Binär-Code, dargestellt an drei Zähleinheiten

Bild 2. ▶

Zerlegung eines Zählschrittes in zwei

Teilschritte. 1. Abfragen des Inhalts des

Hauptspeichers, 2. Einspeichern der neuen Information in den Hauptspeicher. Dieser Vorgang ist mit Hilfe von Schaltern, die wechselweise offen und geschlossen sind, deutlich gemacht [4]

Es 21 Elektronische Zähler

### 2.2 Die Arbeitsmatrix vom JK-Flipflop

Das JK-Flipflop gehört zu den sequentiellen (Folge-)Schaltungen. Bei diesen stellt sich die Ausgangskonfiguration nicht nur nach der anliegenden Eingangskonfiguration ein, sie berücksichtigt auch die vorher vorhanden gewesene Ausgangsoder Eingangskonfiguration. In diesen Fällen vermittelt die Arbeitsmatrix die Kenntnis der sich jeweils einstellenden Ausgangskonfiguration. Tabelle 1 bringt für das JK-Flipflop die Arbeitsmatrix.

Sie macht deutlich, daß für die Zählerfunktion die letzten beiden Zeilen wichtig sind. Legt man an die beiden Eingänge J und K den Signalwert H, so kippt das JK-Flopflop bei jedem Taktimpuls. D. h. am Ausgang Q erscheint

> bei Taktimpuls 1 Signalwert H bei Taktimpuls 2 Signalwert L bei Taktimpuls 3 Signalwert H bei Taktimpuls 4 Signalwert L usw.

Bei der Bedeutung dieses JK-Plipflops erscheint es zweckmäßig, das Zustandekommen seiner Arbeitsmatrix zu verfolgen. Das kann mit Hilfe von Tabelle 2 geschehen. Die Signalkombinationen an den Ausgängen der Gatter und Flipflops lassen sich leicht ermitteln, evtl. empfiehlt es sich, die Arbeitstabelle vom NOR-Flipflop (z. B. in EAB Bd. 11, Es 02, Abschn. 2.2) zu Hilfe zu nehmen.

### 2.3 Das flankengetriggerte JK-Flipflop

Die bisher beschriebene Ausführung des JK-Flipflops hat einen Nachteil, der unter Umständen bedeutsam sein kann. Der Zwischenspeicher ist geöffnet, solange das Taktsignal den Signalwert H hat. In dieser Zeit werden also nicht nur die Nutzeignale in den Zwischenspeicher eingeschrieben, sondern es können auch Störsignale aufgenommen werden. Die so gestörte Information wird dann bei dem darauffolgenden halben Taktschritt in den Hauptspeicher übernommen. Bei solden IK-Flipflops (Master-Slaver.)

net soiten jk-ripijops (Master-Stave-Flipiflops) ist es also wichtig, daß die in den Speicher einzuschreibende Information an den Bedingungs-(Vorbereitungs-) Eingängen anliegt, bevor der Takteingang von L auf H geschaltet wird, und ferner so lange nicht verändert wird, bis

Bild 3. Aufbau eines JK-Flipflops. Q bedeutet: An Q liegt der invertierte Signalwert von Q. Liegt an Q der Signalwert H, so liegt an Q der Signalwert H, so liegt an Q der Signalwert L (gilt auch für C und C). Das besondere Kennzeichen des JK-Flipflops ist die Rückführung: O nach 1 zw. O nach K zw. O nach K zw. O nach K zw. O nach K zw.

Tabelle 1.

|   | J | ĸ  | Signalwe<br>vor<br>dem Tal | nach |

|---|---|----|----------------------------|------|

| a | L | L. | H                          | Н    |

| b | L | H  | H                          | L    |

| C | L | H  | L                          | L    |

| d | L | L  | L                          | L    |

| e | H | L  | L                          | H    |

| f | H | L  | H                          | H    |

| g | H | H  | H                          | L    |

| h | H | H  | L                          | H    |

das Taktsignal von H auf L gegangen und der Zwischenspeicher gesperrt ist. Solche Flipflops bezeichnet man als taktzustandsgesteuert.

Im Gegensatz dazu stehen die taktflankengesteuerten (flankengetriggerten) Flipflops. Bei diesen wird die an den Eingängen liegende Information nur in der Zeitspanne übernommen, in der der Signalwert am Takteingang von L auf H evtl. auch von H auf L) übergeht. Ist die Zeitdauer der triggernden Flanke beendet, ist der Speicher gesperrt, es können also Störungen, die in die Zeitdauer des Signalwertes H fallen, nicht eingespeichert werden.

In EAB Bd. 2, 3.4—4 (Bild 11) oder Es 02 (Bild 9a) ist gezeigt, wie man mit Hilfe einer RC-Kombination, also durch Differenzieren der Impulsflanke, einen Steuerimpuls für das Einspeichern der Information erhalten kann.

Da sich RC-Glieder in integrierten Schaltungen schwer verwirklichen lassen, benützt man hier zur Differenzierung die Kapazität von Halbleitersperrschichten.

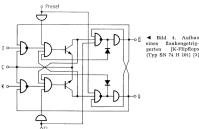

Bild 4 zeigt am Beispiel des SN 74 H 101 den Aufbau eines flankengetriggerten JK-Flipflops. Dem Clock-Eingang wird der Taktimpuls zugeführt. Mit "L" am Clear-Eingang wird der Signalwert am Ausgang Q auf L und am Ausgang Q auf H gebracht, das Flipflop also zurückgesetzt, mit L am Preset-Eingang wird Q auf H, Q auf L gestellt, das Flipflop esectzt.

Dieses Flipflop ist hier als Beispiel gewählt, weil es nicht mit einem statischen Zwischenspieher (wei in Bild 3 geze zeigt), sondern mit einem dynamischen arbeitet. Man verwendet nicht das Master-Slave-Prinzip, bei dem durch Taktimpuls die Information zu festgelegten Zeiten aus dem Zwischen- in den Hauptspeicher gebracht wird, sondern schaltet eine Verzögerung in die Informationskette. Das kann mit Kondensatoren bewirkt werden. Im vorliegenden Fall nutzt man die (Schalt-)Verzögerung der Gatter aus.

Flipflops) ist es also wichtig, daß die in Tabelle 2. JK-Flipflop. Darstellung der Signalkombinationen an den Ein- und Ausgängen den Speicher einzuschreibende Informater der Gatter und Flipflops in Abhängigkeit von den Signal-Konfigurationen an den JK-tion an den Bedingungs-(Vorbereitungs-) Eingängen

|   | -            |    | Schr                | i t t | Schritt 2 |        |    |    |    |    |            |   |   |   |     |   |

|---|--------------|----|---------------------|-------|-----------|--------|----|----|----|----|------------|---|---|---|-----|---|

|   | UND 1 UND 2  |    |                     |       | Flip      | flop 1 | וט | U. | ND | 4  | Flipflop 2 |   |   |   |     |   |

|   | l ₫ c        | E: | KQC                 | Et    | Et Et     | At Az  | Αı | c  | S  | Αŧ | C          | R | s | R | Q   | Ċ |

| a | LLH          | L  | <u>г</u> нн         | L     | L L       | LH     | L  | Н  | L  | н  | н          | н | L | Н | н   |   |

| b | r r h        | L  | ннн                 | н     | L H       | H L    | н  | Н  | Н  | L  | Н          | L | н | L | I.  | I |

| с | <u>г</u> н н | L  | <u>н</u> <u>г</u> н | L     | L L       | H L    | Н  | Н  | н  | L  | н          | L | н | L | L   | 1 |

| d | <u>г</u> н н | L  | ггн                 | L     | L L       | H L    | Н  | Н  | н  | L  | н          | L | н | L | L   | 1 |

| e | н н н        | н  | ггн                 | L     | H L       | LН     | L  | Н  | L  | н  | н          | н | L | н | н   |   |

| f | нгн          | L  | <u>г</u> н н        | L     | L L       | LH     | L  | Н  | L  | н  | н          | н | L | н | Н   |   |

| g | нцн          | L  | н н н               | н     | L H       | H L    | н  | Н  | Н  | L  | н          | L | н | L | , L | 1 |

| h | ннн          | н  | нгн                 | L     | H L       | L H    | L  | Н  | L  | н  | н          | н | L | Н | н   |   |

Unterstrichene Werte: Vorgebene Werte (aus dem vorhergehenden Betriebszustand und den neuen Eingangswerten)

L L bedeutet, daß das Flipflop sich in seiner Speicherstellung befindet (s. EAB Bd. 11, Es 02,

Abschn. 2.2)

Die Buchstaben a...h schaffen die Verbindung zu den Zeilen in Tab. 1

◀ Bild 5. Der 8-4-2-1-BCD-Code

0 0 ò

Ď

Ö

Denör

### 3 Die Zähleinrichtung

Wie bereits in Bild 1 und 2 gezeigt, gehören zu einem Zähler mehrere gleiche Zähleinheiten.

Stelle Wertiake

Die verschiedenen Zähler unterscheiden sich nun voneinander in zwei wichtigen Eigenschaften:

#### a) Verwendeter Zählcode

Es gibt, bedingt durch die unterschiedlichen Rechen- und Anwendungsverfahren, eine große Zahl von Binärcodes, d. h. von Codes, die mit den zwei Binärwerten 0 und 1 arbeiten. Hier wird nur der 8-4-2-1-BCD-Code betrachtet.

Bei diesem erhält, wie Bild 5 zeigt,

die Stelle 1 (Bit 1) die Wertigkeit 26

die Stelle 2 (Bit 2) die Wertigkeit 21

die Stelle 3 (Bit 3) die Wertigkeit 22 die Stelle 4 (Bit 4) die Wertigkeit 23.

Jede Dezimalstelle wird nach diesem Code für sich co-

### b) Asynchrone und synchrone Zähler

Bei den asynchronen Zählern werden die einzelnen Aggregate (Flipflops) nacheinander gesetzt.

D. h. Flipflop 1 steuert Flipflop 2, Flipflop 2 steuert Flipflop 3.

Die Flipflops werden also nacheinander von den Ausgangsimpulsen der in der Zählkette vor ihnen liegenden Flipflops gesteuert.

Im Gegensatz dazu stehen die synchronen Zähler. Bei diesen erhalten alle Flipflops von einem Impulsgeber gleichzeitig den Taktimpuls. Mit ihm werden die Zwischenspeicher geöffnet, so daß die anliegende Information eingespeichert werden kann.

#### 3.1 Asynchroner Zähler für den 8-4-2-1-BCD-Code

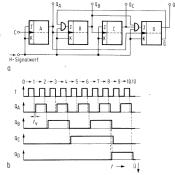

Bild 6g zeigt ein Ausführungsbeispiel. Die Flipflops sind so eingerichtet, daß ieweils bei einem H/L-Übergang, also während der negativen Flanke des am Takteingang C anliegenden Signals, der Speicher gesetzt wird. Damit ergibt sich ein Zählgang nach Bild 6b.

Der Zähler sei durch einen Lösch-Impuls (Clear- oder Reset-Impuls) auf L gesetzt, d. h. an allen Ausgängen Q liegt der Signalwert L.

Am Ende des ersten Zählimpulses (abfallende Flanke) springt QA von L auf H, am Ende des zweiten springt QA von H auf L. Dieser Sprung läßt das Flipflop B kippen, so daß QB von L auf H geht. Am Ende des 4. Impulses geht QA wieder auf L und demzufolge auch QB auf L, gleichzeitig wird durch den Übergang von H auf L am Takteingang von Flipflop C dieses FF gesetzt, sein Ausgang Qc erhält den Signalwert H.

Wichtig sind die Verhältnisse am Ende des 8. Taktimpulses. An QA, QB, QC liegt H. Der H/L-Sprung bewirkt, daß QA auf L geht. Dieser Sprung läßt das Flipflop D kippen, so daß an QD H erscheint. Denn im Moment des H/L-Sprungs liegen sowohl QB als auch QC noch auf H, also an allen Eingängen der UND-Verknüpfung liegt der Signalwert H. Erst mit einer gewissen Verzögerung bewirkt der H/L-Sprung an  $Q_A$  ein Rücksetzen von  $\overline{FF}_B$  ( $\overline{Q}_B$  geht auf L) und, wieder mit der gleichen Verzögerung, an Qc den Signalwechsel auf L.

Nach dem 8. Taktimpuls liegen also

QA, QB, QC auf L und QD auf H.

Wichtig ist noch der 10. Zählimpuls. Am Ende des 9. liegen QA und QD auf H, QB und QC auf L. An der UND-Verknüpfung von  $FF_B$  liegt also, von  $\overline{Q}_D$  kommend, der Signalwert L. Er sperrt das FFB. Am Ende des 10. Zählimpulses geht QA von H auf L. Dieser Sprung bleibt aber auf FFB (wegen dieser Sperre) ohne Einfluß, so daß QB und QC auf L bleiben. Dagegen setzt der Sprung H/L an QA - mit einer gewissen Verzögerung - QD auf L, so daß alle Q-Ausgänge auf L liegen.

Dem Vorteil des einfacheren Aufbaus eines asynchronen Zählers stehen Nachteile gegenüber. Die für jeden Zählimpuls endgültigen Werte stellen sich erst nach einer Verzögerung (bedingt durch den Umschaltvorgang) ein. Diese Verzögerungszeit ist unterschiedlich, je nachdem ob nur die Umschaltung eines oder mehrerer hintereinander geschalteter Flipflops zu berücksichtigen ist. Dadurch wird auch die maximale Zählfrequenz begrenzt.

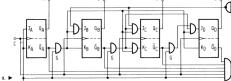

# 3.2 Synchroner Zähler für den 8-4-2-1-BCD-Gode

Der Vorteil ist, daß die beim Durchlauf des Signals entstehende Verzögerung überall nur mit ein und demselben Wert auftritt. D. h. im Prinzip ist die Grenzfrequenz des Zählers durch die Signalverzögerungszeit in einem Flipflop bestimmt. Bei dem in Bild 7 dargestellten Zähleraufbau bedeuten:

C = Takteingang

Cl = Eingang für das Clear-, Lösch- oder Reset-Signal. Liegt an Cl der Signalwert L, werden die Ausgänge Q auf L, der Ausgang Q auf H gesetzt

P = Preset-Eingang

Liegt an P der Signalwert L, werden die Ausgänge Q auf H, der Ausgang Q auf L gesetzt.

Bild 7. Synchroner Einrichtungszähler für den 8-4-2-1-BCD-Code, Vorwärtszähler [3, 4]

Vor die Eingänge JB, JC, KC, JD ist eine UND-Verknüpfung geschaltet.

Die Tabelle 3 gibt die Signalzustände an den einzelnen Ein- und Ausgängen für die Taktschritte 0, 1...10 bzw. 0 an. Sind in einer Spalte für einen Takt zwei Signalwerte aufgeführt, so beziehen sie sich auf die Engänge der vor dem Joder K-Eingang liegenden UND-Verknüpfung.

Ist in dem Zähler Z1 (Dekade 1) der Zählerstand 9 erreicht, so muß mit dem nächsten Zählimpuls der Signalwert H in den Zähler Z2 der nächsthöheren Dekade übertragen werden. Das geschieht, nach Bild 8, in folgender Weise. An den beiden Eingängen des UND-Gatters liegt der Signalwert H, also auch an seinem Ausgang. Nun ist dieser mit den Vorbereitungs-Eingängen J, K des Flipflops A von Z2 verbunden, so daß bei dem nächsten Zählimpuls Z1 auf L geht und Z2 den Übertrag einspeichert.

#### 3.3 Vor- und Rückwärtszähler

Bisher sind in Abschn. 3.1 und 3.2 Vorwärtszähler (also Zähler in einer Richtung, Einrichtungszähler) behandelt worden. Um zu einer Zähleinrichtung zu kommen, die in beiden Richtungen zählen kann, ist es notwendig, in einem solchen Aggregat einen Vor- und einen Rückwärtszähler miteinander zu kombinieren und nach Bedarf jeweils die nicht ge-

wünschte Zählrichtung zu

sperren. Deshalb wird in Bild 9 ein Aufbauschema für einen Rückwärtszähler gebracht und seine Funktion mit Hilfe der Signalzustände an den Ein- und Ausgängen der Flipflops/Gatter erklärt (Tabelle 4).

Die drei UND-Gatter G sind nur dann erforderlich. wenn dieser Rückwärtszähler mit einem Vorwärtszähler kombiniert wird. Denn dann kann bei Vorwärtsbetrieb das Rückwärts-Zählaggregat über den Anschluß Rz durch Anlegen des Signalwerts L gesperrt werden.

Tabelle 3. Synchroner Vorwärtszähler, Darstellung der Signalzustände an den Ein- und Ausgängen der vier Zählereinheiten für die Zählschritte von 0 his 10

| Takt | JA | $K_A$ | $Q_A$ | $J_{\mathrm{B}}$ | $\kappa_{\mathrm{B}}$ | $Q_{\mathrm{B}}$ | $I_{\mathbf{C}}$ | $\kappa_{\rm C}$ | $Q_{\mathrm{C}}$ | $J_{\mathrm{D}}$ | $\kappa_{\mathrm{D}}$ | $Q_{\mathrm{D}}$ | $\overline{\textbf{Q}}_{\textbf{D}}$ | D | С | В | Α |

|------|----|-------|-------|------------------|-----------------------|------------------|------------------|------------------|------------------|------------------|-----------------------|------------------|--------------------------------------|---|---|---|---|

| 0    |    |       | 0     |                  |                       | 0                | Г                |                  | 0                |                  |                       | 0                | 1                                    | 0 | 0 | 0 | 0 |

| 1    | 1  | 1     | 1     | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0                     | 0                | 1                                    | 0 | 0 | 0 | 1 |

| 2    | 1  | 1     | 0     | 1                | 1                     | 1                | 1                | 1                | 0                | 1 0              | 1                     | 0                | 1                                    | 0 | 0 | 1 | 0 |

| 3    | 1  | 1     | 1     | 0                | 0                     | 1                | 0                | 0                | 0                | 0                | 0                     | 0                | 1                                    | 0 | 0 | 1 | 1 |

| 4    | 1  | 1     | 0     | 1                | 1                     | 0                | 1                | 1                | 1                | 1                | 1                     | 0                | 1                                    | 0 | 1 | 0 | 0 |

| 5    | 1  | 1     | 1     | 0                | 0                     | 0                | 0                | 0                | 1                | 1 0              | 0                     | 0                | 1                                    | 0 | 1 | 0 | 1 |

| 6    | 1  | 1     | 0     | 1                | 1                     | 1                | 1                | 1                | 1                | 1                | 1                     | 0                | 1                                    | 0 | 1 | 1 | 0 |

| 7    | 1  | 1     | 1     | 0                | 0                     | 1                | 0                | 0                | 1                | 0                | 0                     | 0                | 1                                    | 0 | 1 | 1 | 1 |

| 8    | 1  | 1     | 0     | 1                | 1                     | 0                | 1                | 1                | 0                | 1                | 1                     | 1                | 0                                    | 1 | 0 | 0 | 0 |

| 9    | 1  | 1     | 1     | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0                     | 1                | 0                                    | 1 | 0 | 0 | 1 |

| 10/0 | 1  | 1     | 0     | 1 0              | 1                     | 0                | 1 0              | 1<br>0           | 0                | 1 0              | 1                     | 0                | 1                                    | 0 | 0 | 0 | 0 |

|      |    |       | 1 🔿   | Sign             | alw                   | ert H            |                  | 0                | ^ S              | Sign             | alwe                  | rt I             | ,                                    |   |   |   |   |

1

Signalwert H

#### Literatur

- Wolf, G.: Digitale Elektronik. Franzis-Verlag, München.

- EAB Bd. 11, Es 02. Franzis-Verlag, München.

- Das TTL-Kochbuch. Texas Instruments Deutschland GmbH, Freising. Dokter, F., und Steinhauer, J.: Digitale Elektronik in der Meßtechnik und Datenverarbeitung Bd. II. Philips Fachbücher. Deutsche Philips

Tabelle 4. Synchroner Rückwärtszähler. Darstellung der Signalzustände an den Ein- und Ausgängen der vier Zählereinheiten

|                      | J | К | $Q_A$ | $\overline{Q}_{A}$ | $J_{\rm I}$ | JōA | $K_{QA}^-$ | $Q_B$ | $Q_{\mathrm{B}}$ | Jį | JOA | $J_{\overline{\mathrm{OB}}}$ | $K_{OA}$ | $K_{\overline{O}B}$ | QC | $\overline{Q}_{C}$ | JOA | JoB | Jōc | $K_{OA}^-$ | $Q_{\mathrm{D}}$ | $Q_D$ | D | С | В | Α |

|----------------------|---|---|-------|--------------------|-------------|-----|------------|-------|------------------|----|-----|------------------------------|----------|---------------------|----|--------------------|-----|-----|-----|------------|------------------|-------|---|---|---|---|

| Anfangs-<br>stellung |   |   | 0     | 1                  |             |     |            | 0     | 1                | Γ  |     |                              |          |                     | 0  | 1                  |     |     |     |            | 0                | 1     | 0 | 0 | 0 | ( |

| 1. Takt              | 1 | 1 | 1     | 0                  | 0           | 1   | 1          | 0     | 1                | 0  | 1   | 1                            | 1        | 1                   | 0  | 1                  | 1   | 1   | 1   | 1          | 1                | 0     | 1 | 0 | 0 | 1 |

| 2. Takt              | 1 | 1 | 0     | 1                  | 1           | 0   | 0          | 0     | 1                | 1  | 0   | 1                            | 0        | 1                   | 0  | 1                  | 0   | 1   | 1   | 0          | 1                | 0     | 1 | 0 | 0 | 6 |

| 3. Takt              | 1 | 1 | 1     | 0                  | 1           | 1   | 1          | 1     | 0                | 1  | 1   | 1                            | 1        | 1                   | 1  | 0                  | 1   | 1   | 1   | 1          | 0                | 1     | 0 | 1 | 1 | 1 |

| 4. Takt              | 1 | 1 | 0     | 1                  | 1           | 0   | 0          | 1     | 0                | 1  | 0   | 0                            | 0        | 0                   | 1  | 0                  | 0   | 0   | 0   | 0          | 0                | 1     | 0 | 1 | 1 | 0 |

| 5. Takt              | 1 | 1 | 1     | 0                  | 1           | 1   | 1          | 0     | 1                | 1  | 1   | 0                            | 1        | 0                   | 1  | 0                  | 1   | 0   | 0   | 1          | 0                | 1     | 0 | 1 | 0 | 1 |

| 6. Takt              | 1 | 1 | 0     | 1                  | 1           | 0   | 0          | 0     | 1                | 1  | 0   | 1                            | 0        | 1                   | 1  | 0                  | 0   | 1   | 0   | 0          | 0                | 1     | 0 | 1 | 0 | 0 |

| 7. Takt              | 1 | 1 | 1     | 0                  | 1           | 1   | 1          | 1     | 0                | 1  | 1   | 1                            | 1        | 1                   | 0  | 1                  | 1   | 1   | 0   | 1          | 0                | 1     | 0 | 0 | 1 | 1 |

| 8. Takt              | 1 | 1 | 0     | 1                  | 1           | 0   | .0         | 1     | 0                | 1  | 0   | 0                            | 0        | 0                   | 0  | 1                  | 0   | 0   | 1   | 0          | 0                | 1     | 0 | 0 | 1 | 0 |

| 9. Takt              | 1 | 1 | 1     | 0                  | 1           | 1   | 1          | 0     | 1                | 1  | 1   | 0                            | 1        | 0                   | 0  | 1                  | 1   | 0   | 1   | 1          | 0                | 1     | 0 | 0 | 0 | 1 |

| 10./0. Takt          | 1 | 1 | 0     | 1                  | 1           | 0   | 0          | 0     | 1                | 1  | 0   | 1                            | 0        | 1                   | 0  | 1                  | 0   | 1   | 1   | 0          | 0                | 1     | 0 | 0 | 0 | C |

Die Bezeichnung  $I_{OA}^{-}$  bedeutet, daß das Signal am J-Eingang vom Q-Ausgang der Zählereinheit A kommt, und Bezeichnung J<sub>I</sub>, daß das Signal am J-Eingang vom Ausgang des Inverters I kommt.

Bild 8. Die Schaltung für den Übertrag von Zählereinheit 1 auf Zählereinheit 2. Hat Z1 die Ziffer 9 gespeichert, steht an Q<sub>A</sub> und Q<sub>D</sub> jeweils der Signalwert H

Bild 9. Þ Synchroner Rückwärtszähler [4]