- País

- Suiza

- Fabricante / Marca

- Albis, Albiswerke AG (Siemens Switzerland AG / Telefunken Zürich AG / Siemens-Albis); Albisrieden

- Año

- 1981

- Categoría

- Signal Processing and Computing

- Radiomuseum.org ID

- 358065

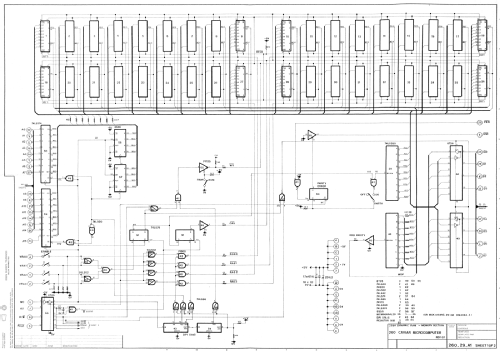

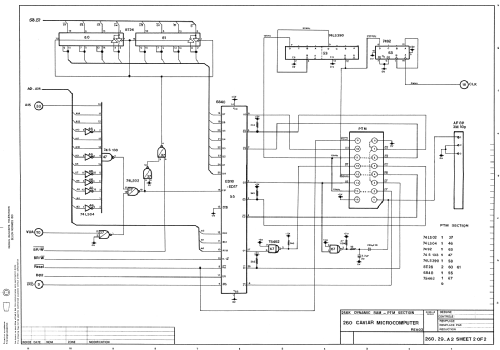

Haga clic en la miniatura esquemática para solicitarlo como documento gratuito.

- Gama de ondas

- - no hay

- Tensión de funcionamiento

- Alimentado desde otro equipo o aparato principal. / DC 5 Volt

- Altavoz

- - - No hay salida de sonido.

- Material

- Printed Circuit Board

- de Radiomuseum.org

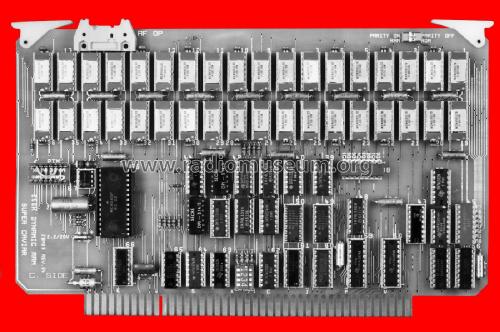

- Modelo: 256K Dynamic RAM 260-29 - Albis, Albiswerke AG Siemens

- Forma

- Chasis (tambien de autoradio)

- Ancho, altura, profundidad

- 248 x 152 x 19 mm / 9.8 x 6 x 0.7 inch

- Anotaciones

-

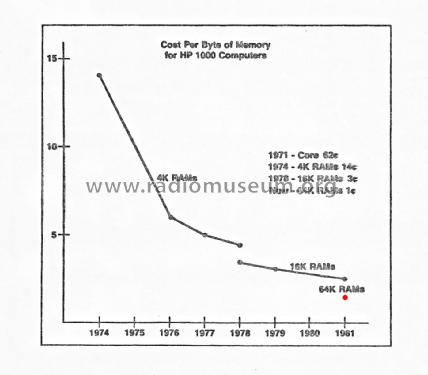

The use of a SuperCAVIAR Converter allowed a 6800-based computer to access up to 256 Kbytes of RAM, comprising 8 sections mapped into 32 Kbytes of the 64 Kbyte address space of the microprocessor. The arrival of the 64 Kbit semiconductor RAM in 1980 was the subject of unusual publicity in circles well beyond the computer electronics world. Market predictions for what was expected to be the industry's first $1000M device spurred the foundation of new enterprises, and promised fortune to those able to overcome the formidable design and manufacturing challenges of a 135,000-element LSI chip.

At that time, about ten manufacturers had devices in full or trial production, with a variety of refresh, speed and power characteristics, while price and availability were highly variable. In spite of the attractive circuit simplification offered by devices promising automatic and self-refresh modes, experience with proprietary products having no second source cautioned the exercise of prudence. So the 260-29 256K dynamic RAM card was based on the use of 'dumb' 64 Kbit chips with externally-generated RAS-only refresh cycles. Both 128-cycle/2ms and 256-cycle/4ms variants can be accommodated.

By generating stable timing signals from multi-tap delay lines, adequate margins are obtained with lowest-cost 250 ns access-time devices, even when undershoot damping is applied and phase 1 of the microprocessor clock cycle is used for fully-transparent hidden refresh operation. The card can be populated, or a fully populated card can be enabled, in increments of 64 Kbytes (2 maps); and the address areas of disabled sections are freed for use by other mapped memory devices, such as a user-program EPROM card.

Separate trees generate write parity and check that of data read. Write protect and parity disable can be selected manually on the RAM card, and parity error interrupts to the MPU (which are non-maskable) can be inhibited by a control signal from the SuperCAVIAR Converter. This facility allows the system firmware to read RAM locations before they have been written, as is required at power-on to distinguish from manual reset. To facilitate interrupt processing, a range of RAM at the lower boundary of each map is common to all of them. The upper limit of the common range is programmable, and can be varied dynamically.

To enhance the speed and flexibility of transfer operations, special modes are provided in which the memory mapping is a function of the direction of the data transfer. The program selection of transfer modes allows the RAM mapping to be modified on a cycle-by-cycle basis. In one mode, microprocessor read operations (including executable code fetches) access the currently selected RAM map, while all write cycles reference RAM 0. In an alternate mode, data are loaded from RAM 0 and automatically stored in the selected mapped RAM. Common RAM mapping overrides transfer mapping in the affected range. To facilitate the development in RAM of assembler-written subroutines which are subsequently to be added to the firmware library, an overlay mode allows an 8 Kbyte address range that is normally occupied by library EPROM to be mapped into part of RAM 0.

To provide audio output and a facility for generating interrupts at programmable time intervals, a multimode triple timer/tone generator is provided on the card. Either chromatic or diatonic scales can be chosen for music output. The timer input is provided from the 6 MHz ADLC clock on the SuperCAVIAR Converter, which is free from the phase stretching applied to the MPU clock during accesses to the floating-point APU.

The 256K Dynamic RAM was designed by Bruce Taylor and manufactured by Siemens-Albis SA from 1981 to 1985.

- Peso neto

- 0.3 kg / 0 lb 10.6 oz (0.661 lb)

- Mencionado en

- -- Original-techn. papers. (Conference Paper May 1981)

- Documentación / Esquemas (1)

- -- Schematic

- Autor

- Modelo creado por Bruce Taylor. Ver en "Modificar Ficha" los participantes posteriores.

- Otros modelos

-

Donde encontrará 176 modelos, 152 con imágenes y 146 con esquemas.

Ir al listado general de Albis, Albiswerke AG (Siemens Switzerland AG / Telefunken Zürich AG / Siemens-Albis); Albisrieden

Colecciones

El modelo 256K Dynamic RAM es parte de las colecciones de los siguientes miembros.