VCXO-PLL 1142-300

Unknown - CUSTOM BUILT: Switzerland (CH)

- Paese

- Svizzera

- Produttore / Marca

- Unknown - CUSTOM BUILT: Switzerland (CH)

- Anno

- 1994–2022

- Categoria

- Elaborazione di segnali e strumenti di calcolo (Computer e moduli SP)

- Radiomuseum.org ID

- 358409

- Numero di transistor

- A semiconduttori.

- Semiconduttori

- Principio generale

- PLL, Phase-locked loop

- Gamme d'onda

- Gamme d'onda nelle note.

- Tensioni di funzionamento

- Fornita mediante altra unità o unità principale. / DC: 15 & -2 & -5.2 Volt

- Altoparlante

- - - Nessuna uscita audio.

- Materiali

- Mobile di metallo

- Radiomuseum.org

- Modello: VCXO-PLL 1142-300 - Unknown - CUSTOM BUILT:

- Forma

- Rack

- Dimensioni (LxAxP)

- 50.6 x 129 x 193 mm / 2 x 5.1 x 7.6 inch

- Annotazioni

-

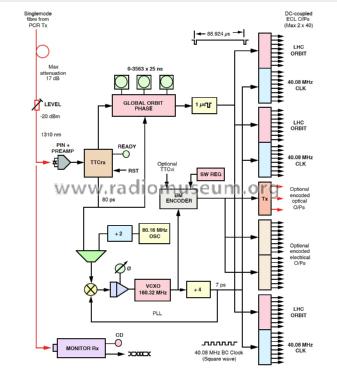

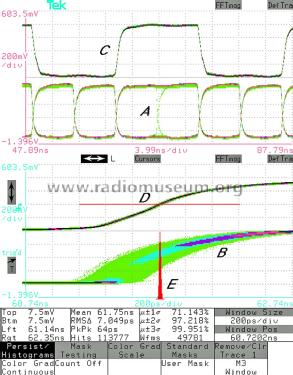

1142-300 VCXO-PLL modules were part of the original system for the transmission of the 40.079 MHz bunch-crossing clock of CERN's Large Hadron Collider (LHC) from the control centre to several thousand front-end electronics destinations at the individual experiments at different locations around the 26.66 km circumference of the machine. The clock was encoded with the 11.2455 kHz LHC Orbit signal and broadcast through optical tree couplers via singlemode optical fibres from laser transmitters in the control centre to LHCrx optical receivers at the experiments. The clock output from the receiver ASIC in the LHCrx has an rms jitter of about 80 ps, and the VCXO-PLL was used to reduce the jitter to about 7 ps before distributing it to the TTCex and TTCtx transmitters of the local Timing, Trigger and Control (TTC) systems of the experiments.

The module uses a low-noise 160.315 MHz Vectron CO-233 Y 3129 VCXO in a PLL with a narrow loop bandwidth, so that the output jitter is determined by the sub-harmonic feedthrough from the fundamental oscillator rather than the noise on the reference signal. It employs an ECL phase comparator/frequency discriminator and achieves low static phase error with an active loop filter based on an IC op amp with very high DC gain.

The VCXO-PLL provides buffered outputs at 160.315 MHz, 80.158 MHz and 40.079 MHz. All the electrical signals at the front panel Lemo connectors are AC-coupled with 10E ECL signal swings, and the internal terminations are 50 Ω to ground. A phase control allows the modules to be accurately matched on a test bench, so that they can be interchanged in the field without any adjustments to the timing being required. Although a local oscillator can be used for test purposes, normally the Reference input is the 40.079 MHz output from an LHCrx module. If the VCXO-PLL is used alone, one of the 40.079 MHz outputs is connected to the Monitor input. However, if the 160.315 MHz output is used to drive a TTC encoder, its 40.079 MHz output can be used instead, so that the encoder electronics is included in the loop. The module operates from 15 V, -2 V and -5.2 V power supplies, and a 12 V supply is derived from the 15 V one internally. It is housed in a standard 3TU 10HP Europa cassette.

The VCXO-PLL was designed by Bruce Taylor in 1991 and manufactured up till 2022. It was initially planned that the LHC would have a bunch crossing frequency of 66.8 MHz. The early VCXO-PLL modules made for that frequency were updated when a bunch-crossing frequency of 40.079 MHz was chosen for the final design of the collider.

- Peso netto

- 0.558 kg / 1 lb 3.7 oz (1.229 lb)

- Bibliografia

- -- Original-techn. papers. (User manual)

- Autore

- Modello inviato da Bruce Taylor. Utilizzare "Proponi modifica" per inviare ulteriori dati.

- Altri modelli

-

In questo link sono elencati 32 modelli, di cui 30 con immagini e 3 con schemi.

Elenco delle radio e altri apparecchi della Unknown - CUSTOM BUILT: Switzerland (CH)